# Novel Approach Towards Performance Enhancement of All Semiconducting Carbon Nanotube Devices for Printed Electronics

Dheeraj Jain, Nima Rouhi, Member, IEEE, Peter J. Burke, Member, IEEE

Department of Electrical Engineering and Computer Science, University of California, Irvine, CA 92697, USA Email: djain@uci.edu, nrouhi@uci.edu, pburke@uci.edu

*Abstract*—Carbon nanotube based semiconducting inks are now being widely used by researchers for several exotic applications including but not limited to flexible TFTs, biosensors and printed electronics. As this point it is crucial to be able to have a precise control over the electronic performance of such devices. In this work, we present our progress towards thin film transistor fabrication where 99% semiconducting nanotubes ink is used as the starting material. By controlling the density of nanotubes in the network, we laid down a road map to predict and enhance the device performance based on their mobility and on/off ratio. From this work the DC analysis of devices characterization shows a mobility more than 90 cm<sup>2</sup>/V-s and also on/off ratios as high as,  $10^5$  have been achieved.

## Index Terms - Carbon Nanotube, Semiconducting Ink.

# I. INTRODUCTION

Semiconducting carbon nanotubes have shown great promises towards high performance semiconducting device applications. Use of such semi-enriched nanotube inks have now paved its pathway for several diverse applications such as high speed field effect (FETs), transistors. transistors thin film chemical/biochemical sensors, nanoelectromechanical systems (NEMS) and electromechanical memory devices. Owing to their small size, high mobility (nearballistic electron transport), high intrinsic cut-off frequency, mechanical and thermal stability, and high current carrying density, nanotube-based devices can be a perfect replacement of silicon-based devices for many applications along with performance enhancement and size reduction. However, a scalable manufacturing technology for nanotube devices with reproducibility and performance in various metrics (mobility, on/off ratio, sensor specificity, etc.) is currently less explored [1]. To date, two of the most widely used techniques for

nanotube device fabrication are "solution-based, deposition of nanotubes" and "in-situ growth". Recent progress in purification techniques has led to the prospects of solution-based techniques to meet unsurpassed performance and increased scalability in printed circuits with the use of all-semiconducting SWNT inks. Although solution-based processing techniques enable the use of presorted semi-enriched nanotubes, limitations are imposed due to the fact that it is almost impossible to get cost- effective 100% pure semiconducting nanotubes in solution. Also the deposition process (e.g. spin-on, ink-jet printed, dropdrying, gravure) and wafer treatment used prior to nanotube deposition play an important role in deciding the performance outcome of such devices. These factors raise the following unanswered questions: Are there any limitations on mobility of a random network of semiconducting nanotubes in relationship to individual nanotubes? Does the density of nanotubes in the network play any role in determining mobility and if so do they also affect the on/off ratio? What are the physical processes that set limits on this scaling?

In general, it is known that the mobility of individual, pristine semiconducting nanotubes can be up to 10,000  $cm^2 V^{-1}s^{-1}$ . However, mobilities for random networks of carbon nanotubes have hovered until recently around the 1 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> limit. The most obvious reason that networks have lower mobilities than individual nanotubes is that tube-tube crossings limit the current flow from source to drain if the channel length is longer than the nanotube length. Increasing the network density can increase the current (and hence potentially the mobility). However the presence of metallic nanotubes can short-circuit the device if the density exceeds the percolation threshold, which means that there is no general theory that explains quantitatively the relationship between mobility, density, and on/off ratio. With this work, we present progress towards semiconducting nanotube network field effect transistors using 99% semiconducting nanotubes as the starting material. We have demonstrated the first

This work was supported by the National Science Foundation, the Army Research Office, the Office of Naval Research, Northrop Grumman and the Korean National Science Foundation (KOSEF) World Class University (WCU) programme.

density-control technique over the nanotube network as a key point to modify the transistor's mobility and on/off ratio [2]. When a dense network mat of nanotubes is deposited, devices outperformed with higher mobility more than 90 cm<sup>2</sup>/V-s, enabling a faster switching speed. In our experiments it was found that relatively thinner mats yielded devices with on/off ratio of more than  $10^5$ , which makes this technique feasible for low power nanoelectronics. In addition, the effect of various gate lengths has been studied which reveals an interesting trend between the channel length and the mobility.

#### II. EXPERIMENTAL

Purified solution of 99% semiconducting-enriched single walled carbon nanotubes (diameter range - 1.2-1.7 nm, length range 300 nm to 5  $\mu$ m) were deposited on top of Si/SiO<sub>2</sub> (300 nm thermally grown oxide) wafer using drop/dry method. Prior to the deposition of nanotubes, the surface of Si/SiO2 wafer was modified with APTES. Following the nanotube deposition, source and drain electrodes (Gate width, 200 µm) were patterned using standard photolithography. Gate length was varied between 10-100 µm, to study the effect of gate length on mobility, on/off ratio, and transconductance for the fabricated devices. E-beam evaporation followed by lift-off process was used to define source and drain electrodes (Pd/Au). For our studies we used Si wafer as the back gate and 300 nm of  $SiO_2$  as the gate dielectric.

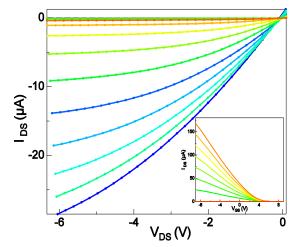

The  $I_D$ - $V_D$  extracted from the dc measurement shows that the current-voltage relationship is linear for small  $V_D$  ranging from -1 V to 1 V (triode region), indicating good ohmic contact between nanotubes and electrodes. By applying more negative  $V_D$  the devices clearly show saturation behavior as showed in the figure below. The gate voltage changes from -10 V (ON state) to +10 V (OFF state). As it can be seen, for  $V_g$  of more than +3 V the devices are in OFF state and the on/off ratio is high enough corresponding to the semiconducting purified nanotube channel. Also in the inset of Fig 1 we present the I<sub>d</sub>- $V_g$  for source-drain voltages from 0 to 7 V.

Fig. 1.  $I_{DS}$ - $V_{DS}$  characteristic of the transistors showing the saturation behavior in p-type transistors, the gate voltage changes from -10 V to +10 V with the 2 V increments. The inset figure demonstrates the  $I_d$  vs  $V_g$  curve of the transistor. The source-drain voltage changes form 0 to -7 V with 1 V increment.

The on/off ratio is more than 100,000 in some devices as expected for all-semiconducting (99%) tubes in the channel. Mobility of more than 90 cm<sup>2</sup>/V-s is also observed using conventional MOSFET equation and curve fitting the  $I_D$ -V<sub>D</sub> characteristic in the triode region.

## **III. DEVICE PERFORMANCE ANALYSIS**

A comprehensive range of nanotube network densities was obtained by varying solution concentration and mobility and on/off ratio of the transistors were mapped for different densities for comparison.

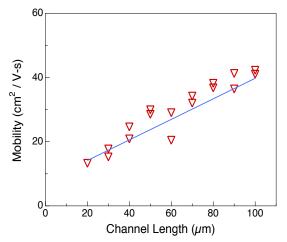

Fig. 2 shows the trend between devices' mobility and their channel length. It is depicted that by increasing the channel length, the mobility increases for 99% semiconducting tubes with a fixed tube density and fixed channel width (200  $\mu$ m).

Fig. 2. Mobility as a function of channel length for a fix and moderate network density.

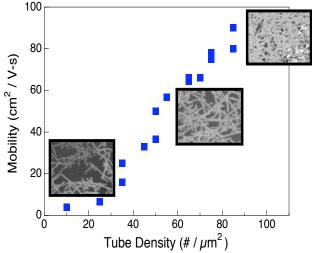

In addition, the density dependence of devices is described below. A comprehensive range of densities from less than 10 tubes/ $\mu$ m<sup>2</sup> to around 90 tubes/ $\mu$ m<sup>2</sup> has been investigated. It was observed that by increasing the network density, the mobility increases (See Fig. 3). This in fact is due to the fact that increasing the density will increase the metallic pathways from source to drain electrode, which eventually results an improvement in the mobility. In addition, the on/off ratio decreases by increasing the network density for the same reason.

Fig. 3. Mobility vs nanotube network density for a wide range of densities from less than 10 tube. $\mu$ m<sup>-2</sup> to around 90 tube. $\mu$ m<sup>-2</sup>. The inset shows SEM image of three different (low, moderate, and high) network densities.

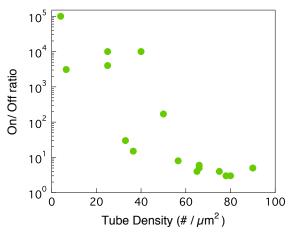

Thus, the relationship between on/off ratio and density has been investigated. The results demonstrate that on/off ratio decreases as the density increases especially for the tube densities of more than 40 tubes per  $\mu m^2$  and the on/off ratio decreases drastically (below 100) as shown in Fig. 4. Results were obtained from transistors with channel length ( $L_{ch}$ ) of 100  $\mu$ m.

Fig. 4. On/off ratio as a function of tube density for a fix channel length of 100  $\mu$ m and channel width of 200  $\mu$ m.

This inverse relationship can be explained by the existence of metallic tubes in the channel. As the density of nanotube network increases, the number of metallic tubes in the channel also goes up hence, the on/off ratio decreases.

#### IV. CONCLUSION

In summary, a strong relationship between the density of the nanotube network and the devices' performance was established. The dc electrical measurements for our TFT devices show a great improvement in terms of mobility (more than 90 cm<sup>2</sup>/V-s) and on/off ratio (more than 100,000), compared to previous works.

# REFERENCES

- N. Rouhi, "Carbon-based Transistors and Nanodevices," Ph.D. Thesis, unpublished, University of California, Irvine, 2011.

- [2] N. Rouhi, et al., "Fundamental Limits on the Mobility of Nanotube-Based Semiconducting," Advanced Materials, vol. 23, pp. 94-99, Jan 4 2011.